Figure 16.5 from Direct-coupled Fet Logic (dcfl) @bullet Source-coupled Fet Logic (scfl) @bullet Advanced Mesfet/hemt Design Examples Iii-v Hbt for Circuit Designers @bullet Current-mode Logic @bullet Emitter-coupled Logic @bullet Ecl/cml Logic Examples @

Amazon.com | ANBOVER Women's High Wedge Beach Summer Thong Platform Slippers, Black, 6US/37EU | Flip-Flops

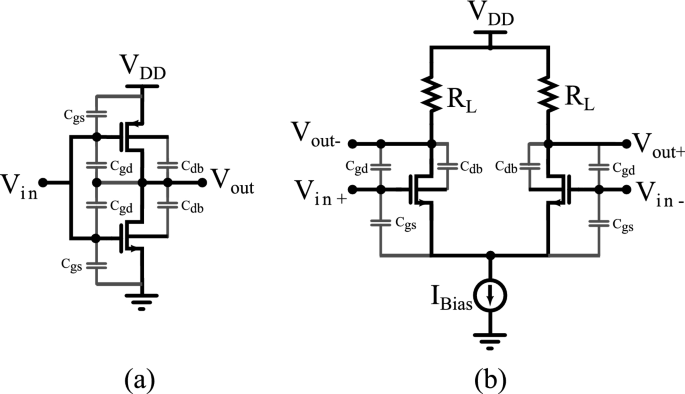

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

Help me calculate the device size of CML/SCL latch design and simulate the gain of it | Forum for Electronics

Amazon.com: MLtuutou Women's Platform Flip Flop with Arch Support, Comfortable Yoga Mat Wedge Flip-Flops, Athletic Walking Thong Slippers for Vacation/Shopping Mall/Wandering/Gathering : Clothing, Shoes & Jewelry